基于FPGA的超聲信號采集系統

發布時間:2017-09-01

1引言

傳統的數據采集系統往往采用單片機或數字信號處理器作為控制器、控制模/數轉換器、存儲器和其他外圍電路,但時鐘頻率較低,各種功能靠軟件的運行來實現,效率較低,難以滿足數據采集系統實時性和同步性的要求。然而基于DSP的數據采集系統,雖然處理速度快,但成本較高,過于頻繁的中斷會使CPU 的效率降低,響應速度變差。采用FPGA為核心設計的采集系統,時鐘頻率高,內部時延小,簡化外圍電路、降低設計風險、縮短開發周期,大大提高了系統的性能,將廣泛用于高速數據采集系統中[1]。本文充分利用FPGA這方面優勢,提出一種基于FPGA的高速超聲信號采集系統,對來自超聲傳感器的高頻信號進行放大、A/D轉換和高速緩存等處理。

2基于FPGA采集系統的設計

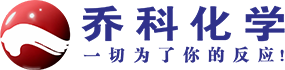

數據采集系統中的控制邏輯單元采用ALTERA公司的EP1C3T144芯片,內部的A/D采樣控制器控制A/DC芯片采集超聲檢測模擬信號,將A/D轉換好的8位數據送到FPGA 內部定制好的RAM 存儲器中存儲。ADC芯片采用美國德州儀器(TI)公司的TLC5510,轉換速率最高可達到50MSPS,換電壓量程為0.6V~2.6V。緩存選用單端口RAM 存儲器,在" MegaWizardPlug-InManager" 內部定制,RAM 的數據寬度和ADC的輸出數據寬度要一致,當RAM 存儲器中完成一個至數個周期的被測信號采樣后,在地址發生器的地址掃描下,將存于RAM 中的數據通過DAC的輸出端進入示波器,完成對FPGA工作狀態的實時觀測和調試,從而可以準確地驗證整個傳輸過程中數據的正確性和時序性是否滿足設計需求。試驗系統中模塊所需的時鐘由全局時鐘CLK直接提供,使能信號由配置的試驗箱上的按鍵Key1控制。系統結構框圖如圖1所示。

2.1ADC控制模塊設計

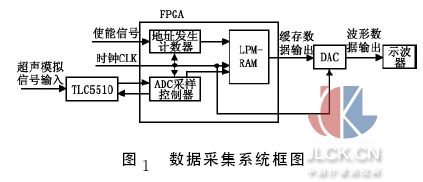

圖2為TLC5510芯片內部功能圖,CLK(時鐘信號)、OE(輸出使能信號)為TLC5510芯片控制信號,與ADC采樣控制器的鏈接見圖2所示。ADC采樣控制器接收到FPGA 系統信號采集使能信號后,啟動TLC5510采集原始數據,超聲模擬信號從ANALOGIN 引腳單端輸入,在轉換時鐘CLK 控制下轉換為8位數字信號,當輸出使能信號OE低電平有效時,轉換后的數字信號D1~D8并行輸出。本文接PIN_16引腳時,通過跳冒來選擇20MHz有源晶振,并打開電源開關為A/D芯片提供電源。

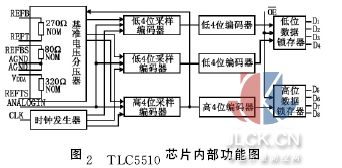

圖3為TLC5510的采樣時序圖,TLC5510是以流水線的工作方式進行工作。當第一個時鐘周期下降沿到來時,模擬輸入電壓將被采樣到高比較器塊和低比較器塊,高比較器塊在第二個時鐘周期的上升沿的最后確定高位數據;同時,低基準電壓產生與高位數據相應的電壓。低比較塊在第三個時鐘周期的上升沿的最后確定低位數據。高位數據和低位數據在第四個時鐘周期的上升沿進行組合。這樣,采樣轉換結果的輸出卻在2.5個CLK周期后送到內部數據總線上。此時如果輸出使能OE有效,轉換后的8位數據就被存儲到RAM 緩沖器中。

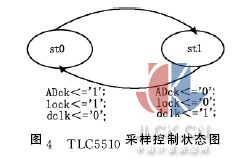

根據采樣時序,用狀態機來描述采樣控制過程。圖4所示為TLC5510采樣控制狀態圖,在狀態st0,給A/D一個采樣時鐘ADck的上升沿,同時鎖存A/D的輸出;在狀態st1。給出采樣控制模塊數據輸出鎖存信號。A/D采樣控制器的輸出共有4個信號:ADck提供采樣時鐘;ADoe為TLC5510的輸出使能,一直有效;data為采樣數據輸出;dclk用來同步data的輸出,作為下一級的data鎖存信號。

2.2RAM 控制模塊設計

存儲器是數據采集系統的重要組成部分,負責將采集后輸出的數字信號進行存儲,以等待下一步操作。QuartusⅡ中含有大量功能強大的LPM 模塊,本文選用FPGA片內的LPM-RAM 宏模塊來實現這種存儲器,輸入和輸出可以支持不同的時鐘或者同一個時鐘來完成A/D轉換輸出的數字信號的緩存和輸出。RAM 控制模塊的連接見圖1所示。

在QuartusⅡ7.2的" MegaWizardPlug-InManager" 設計與定制界面里定制的LPM-RAM模塊,主要是參數的設置,如器件的選擇、數據數量等。本文選擇Cyclone器件,RAM 的數據線寬度8,地址線寬度10,數據數量1024,有一個地址鎖存時鐘和一個寫使能控制線。在存儲容量和采樣速率一定的情況下,定制的RAM 存儲器可檢測的工件厚度最大為30cm(以鋼件作為參考件),滿足一般的管材、棒材和板材檢測。與外掛的SDRAM 相比,內嵌的RAM 集成在FPGA內部,在邏輯設計上更簡單明了,更容易控制和分析,便于進行精確的仿真和調試,充分利用FPGA的資源。

3試驗結果

實驗采用GW48試驗箱,選用電路結構圖NO.5,在QuartusⅡ7.2 開發平臺上建立工程,用VHDL語言編輯數據采集和存儲程序,分配管腳,編譯成功后通過JTAG 下載線下載到試驗箱上。使能信號由試驗箱上的KEY1控制,在KEY1高電平時,每一個CLK 時鐘信號的上升沿完成加一計數,指向下一個RAM 單元,ADC5510 采樣進入RAM,并將采樣的數據存入這個RAM 單元,完成高速數據的緩存。低電平禁止寫入,允許掃描輸出給5651,接示波器上顯示出來,以觀察存入到rom1中的數據信息是否與超聲信號相似,評價該采樣系統的性能。由于用到的D/A 芯片是超高速、10位分辨率的THS5651,所以將其低兩位賦0。

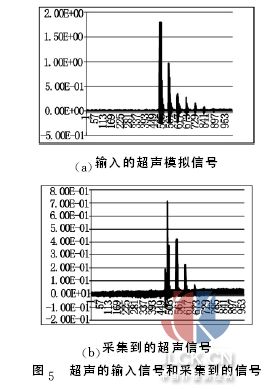

圖5為采樣前輸入超聲信號波形和采樣后的超聲信號波形圖。通過對比采樣前后的超聲波形可以發現,輸入超聲信號能看到很多次底波,而采樣后的信號只能看到二次底波和正的幅值。這是因為超聲信號里含有很多噪聲信號,采樣過程中底波信號的電壓比較小時會被噪聲信號覆蓋,而且示波器本身也有很多噪聲信號,當輸入的超聲信號的電壓很小時,也會把超聲信號覆蓋,且由A/D模塊的輸入電壓范圍決定系統只能采集0.6V~2.6V 之間的超聲信號波形。但該數據采集系統實現了超聲信號的高速采樣和緩存過程,將超聲信號轉換為數字信號處理,可以提高對缺陷定位、定量的精度。

4結束語

基于FPGA 的超聲信號采集系統實現了超聲信號的超高速采集和存儲,但還需要做好噪聲信號處理方面的問題,如對信號進行濾波處理,防止超聲信號被覆蓋等。若存儲數據量很大時,因FPGA內部存儲資源有限,還需要擴展外部的存儲資源,應注意時序的控制使傳輸速度之間協調。

摘自:中國計量測控網