首頁>技術中心>技術資訊>可編程邏輯器件在超聲波流量計中的應用

可編程邏輯器件在超聲波流量計中的應用

發布時間:2017-09-01

1引言

硬件描述語言HDL的出現使得數字系統的硬件構成及其行為完全可以用HDL語言來描述和仿真。這樣,不熟悉硬件電路設計的人員同樣可以借助HDL語言,設計出符合要求的硬件系統。不僅如此,利用HDL語言來設計系統硬件與傳統的設計方法相比,還有許多突出的優點。HDL技術的引入必將是數字系統設計領域的一次革命。最早的可編程邏輯器件是采用TTL工藝生產的一次性可編程的PLA、PAL器件,它們只能實現一些簡單的邏輯功能。隨著可編程技術的不斷發展,可編程器件的集成度和性能都有了很大的提高。

Altera公司最新推出的ACEX 1K PLD系列最多可含257 000個系統門,工作速度在115 MHz以上,可以完成一定的存儲功能和各種復雜的邏輯功能,包括DSP糾錯、寬帶數據處理、微處理器應用以及數據傳輸等功能。設計采用的ispLSI 1032 80LJ84芯片,工作速度為80 MHz,有84個引腳,其中I/O引腳64個,內部包含有6000個PLD門,固定傳輸延遲是4.5ns,可重復編程10 000次以上;此外,ispLSI為在系統可編程器件,可不用編程器而直接在已設計好的目標系統或線路板上進行編程,想改變設計也十分方便。

2VHDL與開發軟件Workview Office

大多數ASIC研制和生產廠家都開發了用于自己目的硬件描述語言,其中最有影響力的當屬美國國防部開發的VHDL(Very High Speed Integrated CircuitHDL)和Verilog公司開發的Verilog HDL,兩者都已被確定為IEEE國際標準。設計中使用的是VHDL語言,開發軟件是Lattice公司提供的isp-VHDL View-logic系統。isp-VHDL是進行電子系統設計的強有力工具,它的使用可以大大提高設計的效率和產品的性能。這套軟件由Viewlogic Workview Office和is-pDS+綜合―優化邏輯軟件兩部分組成,具有強大的VHDL綜合、原理圖輸入、功能與時序仿真、ispDS+適配器和isp-DOWNLOAD(菊花鏈下載)能力。

3系統硬件電路的集成化設計

超聲波流量計硬件電路的結構十分復雜,所需分立件的數量較大,這給系統的設計和調試帶來了很大的難度。將硬件電路中完成數字功能的大部分器件都集成到ispLSI 1032器件中去,大大降低了系統硬件的設計難度。

3?1計數器部分的集成化設計

計數電路的精度和穩定性對超聲波流量計的整體性能至關重要。共使用8個計數器,4個用于計時電路,4個用于分頻電路。其中,兩個主計數器的長度為21位,編程有各自的片選、時鐘輸入、讀信號、輸出位數選擇、計數使能和數據輸出等端口。輸出位數選擇信號的作用是提高ispLSI器件I/O引腳的利用率,21位的計數值分3次由同一個8位數據端口輸出,計數值的0~7位、8~15位、16~20位對應的輸出選擇信號分別是00、01、10,11為禁止狀態。計數器的位長和控制信號還可以根據需要靈活設置。

3?2窗口電路的集成化設計

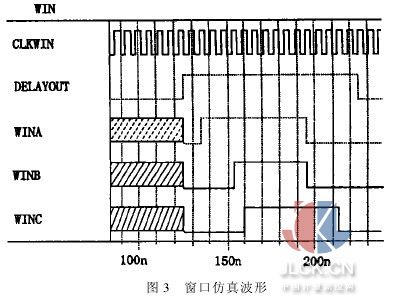

時鐘窗口的設置限定了接收超聲波信號的時間范圍,是消除噪聲影響的重要手段。傳統的窗口電路一般由單穩態觸發器實現,窗口的寬度由外接電阻和電容的值決定,調整起來很不方便,輸出波形也不夠理想。采用集成化設計后,窗口的起始位置和寬度都由使用同一個時鐘的不同計數器的計數值來控制,精度大大提高。而且由于窗口是由數字電路產生的,所以波形也非常好。窗口電路的功能仿真波形如圖3所示。其中CLKWIN是時鐘信號,DELAYOUT是延時計數器的輸出,用來限定窗口的范圍,WINA、WINB、WINC是用于控制功能的3個窗口。

3?3觸發器和邏輯器件的集成化設計

觸發器和各種邏輯器件集成到ispLSI中相對比較容易。可以根據需要靈活地設置觸發器的種類和形式,如是否有置位復位端,是同步還是異步等。邏輯功能的實現只要給出輸入輸出端口和它們之間的邏輯表達式就行了。

4結論

PLD器件的應用,使超聲波流量計硬件電路設計中所用IC器件的數量明顯減少。用兩片ispLSI 1032實現了原設計中約30片IC的功能,不僅減小了設計電路板的面積,同時提高了系統的穩定性和設計靈活性。

摘自:中國計量測控網